## 数字逻辑电路

# 组合逻辑电路的分析与设计

#### 西安交通大学

电子物理与器件教育部重点实验室等离子体与微波电子学研究所

张小宁

# 数字逻辑基础

- 1. 逻辑电路文档标准

- 2. 组合逻辑电路的分析与设计

- 3. 组合逻辑电路中的竞争与险象

- 4. 常用的MSI组合逻辑器件及其应用

### 组合逻辑电路的分析与设计

# 什么是组合逻辑和时序逻辑,Why?

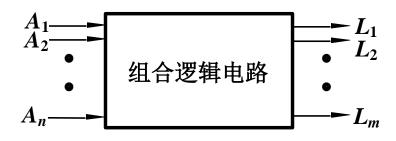

组合逻辑电路的定义

组合逻辑电路的一般框图

$$L_i = f(A_1, A_2, ..., A_n)$$

(i=1, 2, ..., m)

#### 结构特征:

- 1、输出、输入之间没有反馈延迟通路,

- 2、不含记忆单元

#### 工作特征:

在任何时刻, 电路的输出状态只取决于同一时刻的输入状态而与电路原来的状态无关。

## 组合逻辑电路的分析与设计

#### 1. 组合逻辑电路的分析

根据给定电路,分析该电路输出与输入之间的逻辑关系,得出电路的逻辑功能的描述,进而评估此电路的性能,还可进一步改进电路。

- (1) 表达式法:利用表达式分析电路

- (2) 穷举法: 利用真值表分析电路

一般情况下是二者的结合运用。

#### 组合逻辑电路的分析步骤:

- (1) 由逻辑图写出各输出端的逻辑表达式;

- (2) 化简和变换逻辑表达式;

- (3) 列出真值表; 画出波形图;

- (4) 根据真值表或逻辑表达式,经分析最后确定其功能。

例1. 根据电路逐级写出各门的输出表达式,直至写出输出逻辑表达式。

P1=

$$\overline{AB}$$

P2= $\overline{A}$  + C

P3=B $\oplus$   $\overline{C}$

P4=P1P3= $\overline{AB}$   $\overline{\overline{A}}$  + C

F= $\overline{P3}$  + P4 = B $\oplus$  C

这是输出函数F的最简表达式,该电路实现了两个变量B和C的异或运算。

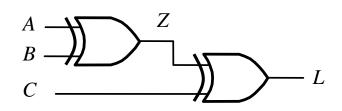

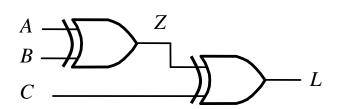

#### 例2 分析如图所示逻辑电路的功能。

解: 1.根据逻辑图写出输出函数的逻辑表达式

$$L = Z \oplus C$$

$$= (A \oplus B) \oplus C$$

$$= A \oplus B \oplus C$$

- 2. 列写真值表。

- 3. 确定逻辑功能:

输入变量的取值中有奇数个1时, L为1, 否则L为0,电路具有为奇 校验功能。

| A | В | C | $Z = A \oplus B$ | $L = (A \oplus B \oplus C)$ |

|---|---|---|------------------|-----------------------------|

| 0 | 0 | 0 | 0                | 0                           |

| 0 | 0 | 1 | 0                | 1                           |

| 0 | 1 | 0 | 1                | 1                           |

| 0 | 1 | 1 | 1                | 0                           |

| 1 | 0 | 0 | 1                | 1                           |

| 1 | 0 | 1 | 1                | 0                           |

| 1 | 1 | 0 | 0                | 0                           |

| 1 | 1 | 1 | 0                | 1                           |

如要实现偶校验, 电路应做何改变?

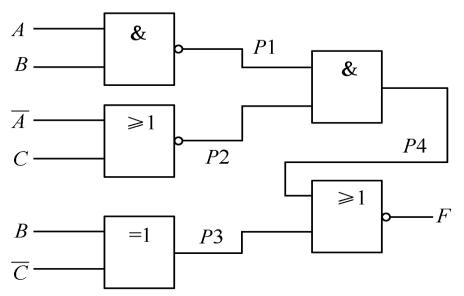

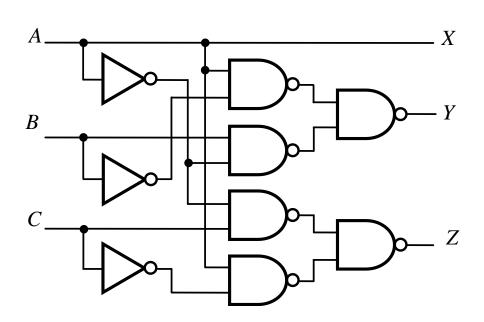

#### 例3 试分析下图所示组合逻辑电路的逻辑功能。

解: (1) 根据逻辑电路写出各输出端的逻辑表达式,并进行化简和变换。

$$X = A$$

$$Y = \overline{\overline{A}\overline{B} \cdot \overline{\overline{A}}B}$$

$$Z = \overline{\overline{A}\overline{\overline{C}} \cdot \overline{\overline{A}}C}$$

# (2) 列写真值表

$$X = A$$

$$Y = \overline{\overline{A}\overline{B} \cdot \overline{\overline{A}B}} = A\overline{B} + \overline{A}B$$

$Z = \overline{A\overline{C} \cdot \overline{AC}} = A\overline{C} + \overline{AC}$

# 真值表

| $\boldsymbol{A}$ | В | C | X | Y | Z |

|------------------|---|---|---|---|---|

| 0                | 0 | 0 | 0 | 0 | 0 |

| 0                | 0 | 1 | 0 | 0 | 1 |

| 0                | 1 | 0 | 0 | 1 | 0 |

| 0                | 1 | 1 | 0 | 1 | 1 |

| 1                | 0 | 0 | 1 | 1 | 1 |

| 1                | 0 | 1 | 1 | 1 | 0 |

| 1                | 1 | 0 | 1 | 0 | 1 |

| 1                | 1 | 1 | 1 | 0 | 0 |

#### (3) 确定电路逻辑功能

#### 电路逻辑功能:

- a) 对输入的二进制码求反码。

- b) 最高位为符号位,0表示正数, 1表示负数

- c) 正数的反码与原码相同;

- d) 负数的数值部分是在原码的 基础上逐位求反。

# 真值表

| $oldsymbol{A}$ | В | C | X | Y | Z |

|----------------|---|---|---|---|---|

| 0              | 0 | 0 | 0 | 0 | 0 |

| 0              | 0 | 1 | 0 | 0 | 1 |

| 0              | 1 | 0 | 0 | 1 | 0 |

| 0              | 1 | 1 | 0 | 1 | 1 |

| 1              | 0 | 0 | 1 | 1 | 1 |

| 1              | 0 | 1 | 1 | 1 | 0 |

| 1              | 1 | 0 | 1 | 0 | 1 |

| 1              | 1 | 1 | 1 | 0 | 0 |

穷举法的结果是真值表。即列出n个输入变量的所有2<sup>n</sup>个输入组合,并根据每一个输入组合决定所有门的输出,逐级推出电路的输出,得到真值表。

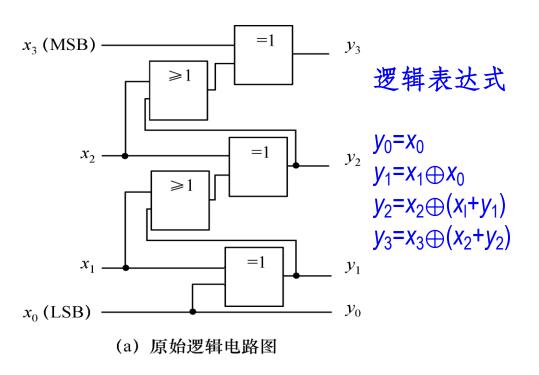

例4:分析如下图(a)四输入输出的逻辑电路。

从真值表中可以看出,每一组输入组合与其所对应的输出组合之间是"按位取反加一"的关系,如输入组合1100,则所对应的输出组合是0100,因此本电路是一个4位二进制求补电路,或称对16求补器。

| $x_3 \ x_2 \ x_1 \ x_0$ | $y_3 \ y_2 \ y_1 \ y_0$ |

|-------------------------|-------------------------|

| 0 0 0 0                 | 0 0 0 0                 |

| 0 0 0 1                 | 1 1 1 1                 |

| 0 0 1 0                 | 1 1 1 0                 |

| 0 0 1 1                 | 1 1 0 1                 |

| 0 1 0 0                 | 1 1 0 0                 |

| 0 1 0 1                 | 1 0 1 1                 |

| 0 1 1 0                 | 1 0 1 0                 |

| 0 1 1 1                 | 1 0 0 1                 |

| 1 0 0 0                 | 1 0 0 0                 |

| 1 0 0 1                 | 0 1 1 1                 |

| 1 0 1 0                 | 0 1 1 0                 |

| 1 0 1 1                 | 0 1 0 1                 |

| 1 1 0 0                 | 0 1 0 0                 |

| 1 1 0 1                 | 0 0 1 1                 |

| 1 1 1 0                 | 0 0 1 0                 |

| 1 1 1 1                 | 0 0 0 1                 |

#### 组合电路性能评价

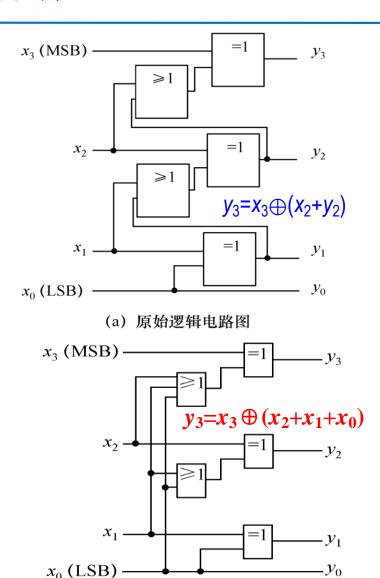

分析上图所示逻辑电路的性能,并给出评价,提出改进建议。

解:将左面的4个表达式作些变换,变换如右:

$$y_0 = x_0$$

$y_1 = x_1 \oplus x_0$

$y_2 = x_2 \oplus (x_1 + y_1)$

$y_3 = x_3 \oplus (x_2 + y_2)$

$y_0 = x_0$

$y_1 = x_1 \oplus x_0$

$y_2 = x_2 \oplus (x_1 + x_0)$

$y_3 = x_3 \oplus (x_2 + x_1 + x_0)$

上面这组表达式意味着求补器的设计依据的是:

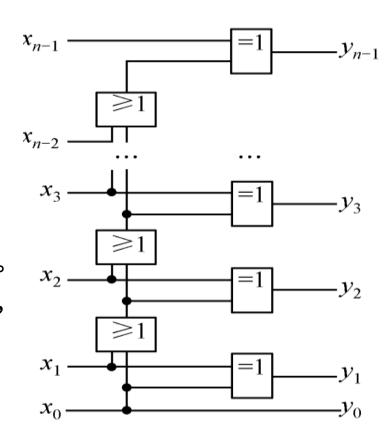

$$y_i = x_i \oplus (x_{i-1} + \cdots + x_1 + x_0), 1 \le i \le n-1.$$

$X_i$ 是否变反由低位决定,低位全是 $0X_i$ 不变,表示了求补器的逻辑规律。

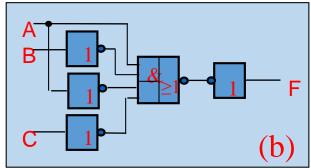

表达式变换后所对应的电路结构如图(c)。图(a) 所示电路是一个串行电路,图(c)所示电路是一个并 行电路。

一般来说,串行电路结构比较简单,但运行速度比较慢。并行电路结构相对较为复杂,但运行速度快。

图(a)所示电路,除了低位为,为,每增加一位输入,对应的输出位电路只需增加一个异或门和一个或门,结构完全是一致的;

图(c)所示电路,每个或门的输入端引线都不一样,越到高位其输入端引线越多,这不仅破坏了各位结构的统一,也增加了电路成本,并受限于或门的输入数而使位数n的扩充变得困难。

(c) 改进后的并行电路

针对该问题,将表达式再作变换如下:

$$y_0 = x_0$$

$y_1 = x_1 \oplus x_0$

$y_2 = x_2 \oplus (x_1 + x_0)$

$y_3 = x_3 \oplus (x_2 + (x_1 + x_0))$

$y_i = x_i \oplus (x_{i-1} + \dots + (x_2 + (x_1 + x_0)) \dots), (0 \le i \le n-1)$

该组表达式所对应的电路图如图(d)所示。 该电路继承了图(a)和图(c)所示电路的优点, 保留了各位结构统一的特点,但其运行速 度快于图(a)而又慢于图(c)所示电路。该电 路使用了较多器件,因而这是一种折中的 结果。

在实际设计中,希望的是提高运行速度。 因此,并行电路使用更广泛。

(D) 结合前两种电路所得电路

#### 2. 组合电路设计

目的:根据要实现的逻辑功能,利用逻辑代数方法实现逻辑电路设计。

要求: 电路用最少的逻辑门(集成块)、最少的输入端数。

#### 组合逻辑电路的设计步骤

(1) 分析设计要求 确定输入、输出的变量;逻辑关系;有无d(无关项) (2) 列出真值表 填入卡诺图进行化简 (3) 写出最简逻辑表达式 由卡诺图得到最简与或式 (4) 表达式变换 根据所选用门的类型;输入无反变量;有效级等。

(5) 画出电路逻辑图

例1 某火车站有特快、直快和慢车三种类型的客运列车进出,试设计一个指示列车等待进站的逻辑电路,当有两种或以上的列车等待进站时,要求发出信号,提示工作人员安排进站事宜。

解: (1) 分析设计要求

输入信号: A、B、C分别表示特快、直快和慢车,且有进站请求时为1,没有请求时为0。

输出信号: L表示进站状况,有两种以上的车进站为1,否则为0。

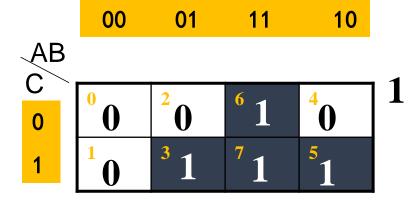

(2) 列出真值表,填写卡诺图

(3) 写出逻辑表达式, 化简。

|   | 输。 | 输出       |   |

|---|----|----------|---|

| A | В  | <b>C</b> | L |

| 0 | 0  | 0        | 0 |

| 0 | 0  | 1        | 0 |

| 0 | 1  | 0        | 0 |

| 0 | 1  | 1        | 1 |

| 1 | 0  | 0        | 0 |

| 1 | 0  | 1        | 1 |

| 1 | 1  | 0        | 1 |

| 1 | 1  | 1        | 1 |

$$L = \overline{ABC} + A\overline{BC} + AB\overline{C} + ABC$$

$$L=AB+AC+BC$$

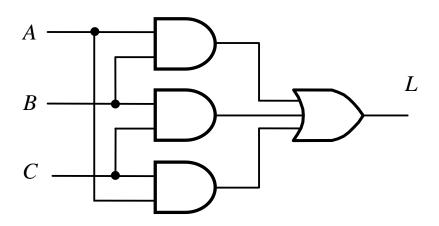

(4) 根据输出逻辑表达式画出逻辑图。

$$L=AB+AC+BC$$

表达式为最简与或式,用与门和或门实现两级"与-或"结构的 最简电路如图。

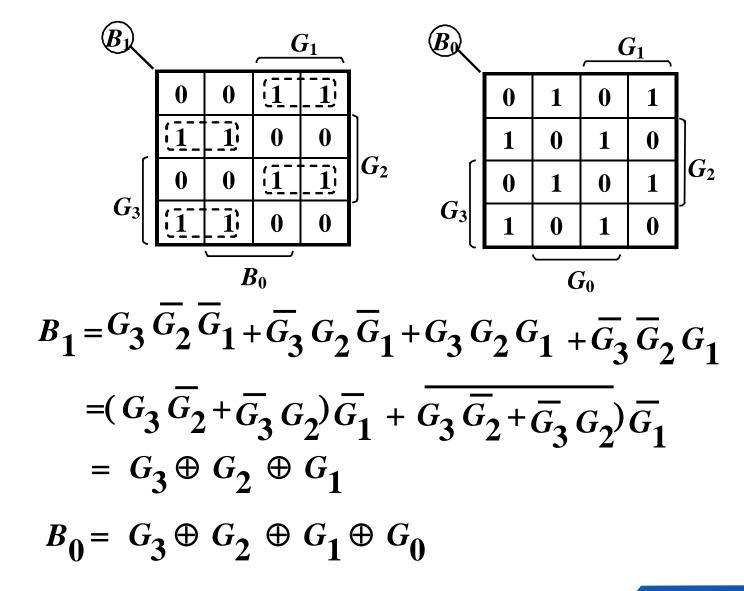

例2 试设计一个码转换电路,将4位格雷码转换为自然二进制码。可以采用任何逻辑门电路来实现。

解: (1) 明确逻辑功能,列出真值表。

设输入变量为 $G_3$ 、 $G_2$ 、 $G_1$ 、 $G_0$ 为格雷码,

输出变量 $B_3$ 、 $B_2$ 、 $B_1$ 和 $B_0$ 为自然二进制码。

当输入格雷码按照从0到15递增排序时,可列出逻辑电路真值表

18/44

#### 逻辑电路真值表

| 输入                | 输出                | 输入                | 输出                |

|-------------------|-------------------|-------------------|-------------------|

| $G_3 G_2 G_1 G_0$ | $B_3 B_2 B_1 B_0$ | $G_3 G_2 G_1 G_0$ | $B_3 B_2 B_1 B_0$ |

| 0 0 0 0           | 0 0 0 0           | 1 1 0 0           | 1 0 0 0           |

| 0 0 0 1           | 0 0 0 1           | 1 1 0 1           | 1 0 0 1           |

| 0 0 1 1           | 0 0 1 0           | 1 1 1 1           | 1 0 1 0           |

| 0 0 1 0           | 0 0 1 1           | 1 1 1 0           | 1 0 1 1           |

| 0 1 1 0           | 0 1 0 0           | 1 0 1 0           | 1 1 0 0           |

| 0 1 1 1           | 0 1 0 1           | 1 0 1 1           | 1 1 0 1           |

| 0 1 0 1           | 0 1 1 0           | 1 0 0 1           | 1 1 1 0           |

| 0 1 0 0           | 0 1 1 1           | 1 0 0 0           | 1111              |

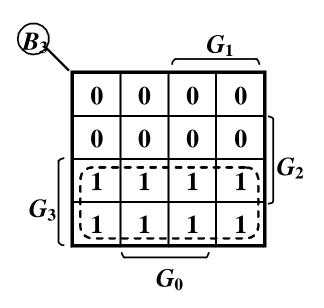

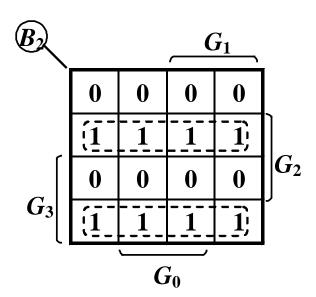

(2) 画出各输出函数的卡诺图,并化简和变换。

$$B_3 = G_3$$

$$B_2 = G_3 \overline{G}_2 + \overline{G}_3 G_2$$

$$= B_3 \oplus G_2$$

21/44

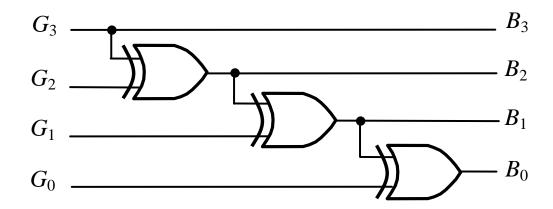

#### (3) 根据逻辑表达式, 画出逻辑图

用异或门代替与门和或门能使逻辑电路比较简单。考虑相同乘积项 可以减少门电路数目,降低实现电路的成本。

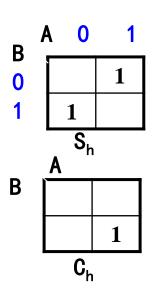

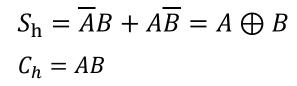

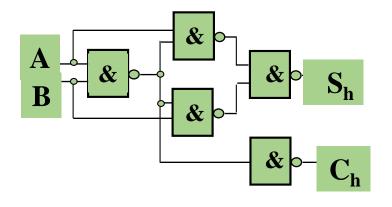

#### 例3 半加器 Half-Adder

输入变量: 加数A、B

输出函数:和Sh、进位Ch

| A B | $S_h C_h$ |

|-----|-----------|

| 0 0 | 0 0       |

| 0 1 | 1 0       |

| 1 0 | 1 0       |

| 1 1 | 0 1       |

二级与或电路

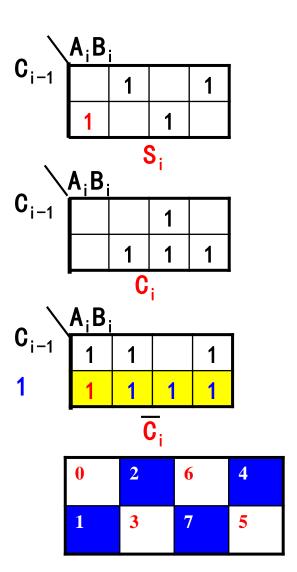

#### 例4 全加器Full-Adder

输入变量:被加数  $A_i$ 、加数  $B_i$ 、来自低位的进位  $C_{i-1}$

输出函数:本位和Si、本位向高位的进位Ci

| Ai | B <sub>i</sub> ( | Si | C <sub>i</sub> |   |

|----|------------------|----|----------------|---|

| 0  | 0                | 0  | 0              | 0 |

| 0  | 0                | 1  | 1              | 0 |

| 0  | 1                | 0  | 1              | 0 |

| 0  | 1                | 1  | 0              | 1 |

| 1  | 0                | 0  | 1              | 0 |

| 1  | 0                | 1  | 0              | 1 |

| 1  | 1                | 0  | 0              | 1 |

| 1  | 1                | 1  | 1              | 1 |

| $A_iB_i$                                                           | $A_iB_i$                  |                      | _  |         | _            |

|--------------------------------------------------------------------|---------------------------|----------------------|----|---------|--------------|

| $C_{i-1}$ $1$ $1$                                                  | U <sub>i−1</sub>          |                      | 1  |         |              |

| 1 1                                                                |                           | 1                    | 1  | 1       |              |

| Si                                                                 |                           | C                    | i  |         |              |

| $S_i = A_i \oplus B_i \oplus C_{i-1}$                              |                           |                      |    |         |              |

| $= \overline{A_i B_i} C_{i-1} + \overline{A_i} B_i \overline{C_i}$ | $_{-1}+A_{i}\overline{B}$ | $\overline{C}_{i-1}$ | 1+ | $A_i I$ | $B_iC_{i-1}$ |

| $C_{i} = A_{i}B_{i} + A_{i}C_{i-1} +$                              | $B_iC_{i-1}$              |                      |    |         |              |

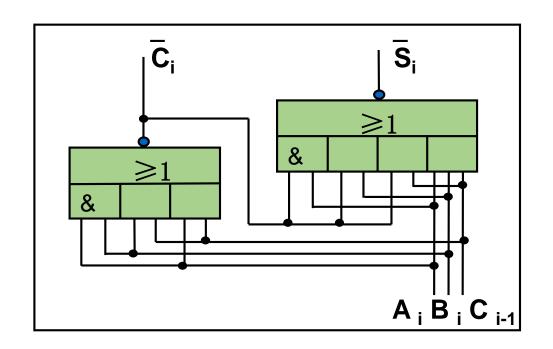

#### 用"与或非"门实现全加器

$$\frac{C_{i}}{C_{i}} = A_{i}B_{i} + A_{i} C_{i-1} + B_{i} C_{i-1}$$

$$S_{i} = m_{1} + m_{2} + m_{4} + m_{7} \qquad \text{为了使用原变量}$$

$$m_{1} = C_{i-1} \cdot \overline{C_{i}}$$

$$m_{2} = B_{i} \cdot \overline{C_{i}}$$

$$m_{4} = A_{i} \cdot \overline{C_{i}}$$

$$m_{7} = A_{i} \cdot B_{i} \cdot C_{i-1}$$

#### $S_i = \overline{A_i B_i} C_{i-1} + \overline{A_i} B_i \overline{C}_{i-1} + \overline{A_i} \overline{B_i C}_{i-1} + \overline{A_i} B_i \overline{C}_{i-1}$

故

$$S_i = C_{i-1} \cdot \overline{C_i} + B_i \cdot \overline{C_i} + A_i \cdot \overline{C_i} + A_i \cdot B_i \cdot C_{i-1}$$

=  $\overline{C_i} \cdot (C_{i-1} + B_i + A_i) + A_i \cdot B_i \cdot C_{i-1}$

#### 用"与或非"门实现全加器

$$\overline{C_i} = \overline{A_i B_i + A_i C_{i-1} + B_i C_{i-1}}$$

$$\overline{S_i} = \overline{\overline{C_i} \cdot (C_{i-1} + B_i + A_i) + A_i \cdot B_i \cdot C_{i-1}}$$

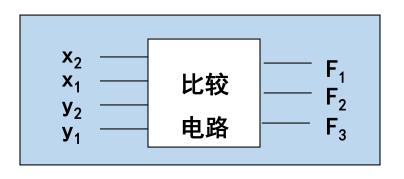

例5 比较器:Comparators

输入变量: 两个正整数  $x = x_2x_1$ ,  $y = y_2y_1$

输出函数:

三个比较结果

F1(x > y), F2(x < y), F3(x = y)

①根据先比较高位后比较低位的原则,列出使函数为1的简化真值表:

#### 为什么要按位分开写真值表?

| <b>x</b> <sub>2</sub> | <b>y</b> <sub>2</sub> | <b>x</b> <sub>1</sub> | <b>y</b> <sub>1</sub> |   | F <sub>1</sub> | F <sub>2</sub> | F <sub>3</sub> |

|-----------------------|-----------------------|-----------------------|-----------------------|---|----------------|----------------|----------------|

| 1                     | 0                     | d                     | d                     |   | 1              | 0              | 0              |

| 0                     | 1                     | d                     | d                     | ( | 0              | 1              | 0              |

|                       |                       | 1                     | 0                     |   | 1              | 0              | 0              |

|                       | 0                     | 0                     | 1                     | ( | 0              | 1              | 0              |

| 0                     | 0                     | 0                     | 0                     | ( | 0              | 0              | 1              |

|                       |                       | 1                     | 1                     | ( | 0              | 0              | 1              |

|                       |                       | 1                     | 0                     |   | 1              | 0              | 0              |

| 1                     | 4                     | 0                     | 1                     | ( | 0              | 1              | 0              |

| '                     | 1                     | 0                     | 0                     | ( | 0              | 0              | 1              |

|                       |                       | 1                     | 1                     |   | 0              | 0              | 1              |

#### ②由简化真值表直接写出逻辑表达式:

$$F_{1} = x_{2}\overline{y}_{2} + \overline{x}_{2}\overline{y}_{2}x_{1}\overline{y}_{1} + x_{2}y_{2}x_{1}\overline{y}_{1}$$

$$F_{2} = \overline{x}_{2}y_{2} + \overline{x}_{2}\overline{y}_{2}\overline{x}_{1}y_{1} + x_{2}y_{2}\overline{x}_{1}y_{1}$$

$$F_{3} = \overline{x}_{2}\overline{y}_{2}\overline{x}_{1}\overline{y}_{1} + \overline{x}_{2}\overline{y}_{2}x_{1}y_{1}$$

$$+ x_{2}y_{2}\overline{x}_{1}\overline{y}_{1} + x_{2}y_{2}x_{1}y_{1}$$

逻辑电路图参见教材P58图2.28(c)。

| x <sub>2</sub> | y <sub>2</sub> | <b>x</b> <sub>1</sub> | у <sub>1</sub>   | F <sub>1</sub>   | F <sub>2</sub>   | F <sub>3</sub>   |

|----------------|----------------|-----------------------|------------------|------------------|------------------|------------------|

| 1              | 0              | d                     | d                | 1                | 0                | 0                |

| 0              | 1              | d                     | d                | 0                | 1                | 0                |

| 0              | 0              | 1<br>0<br>0<br>1      | 0<br>1<br>0<br>1 | 1<br>0<br>0<br>0 | 0<br>1<br>0<br>0 | 0<br>0<br>1<br>1 |

| 1              | 1              | 1<br>0<br>0<br>1      | 0<br>1<br>0<br>1 | 1<br>0<br>0<br>0 | 0<br>1<br>0<br>0 | 0<br>0<br>1<br>1 |

由逻辑问题描述直接写出逻辑表达式。

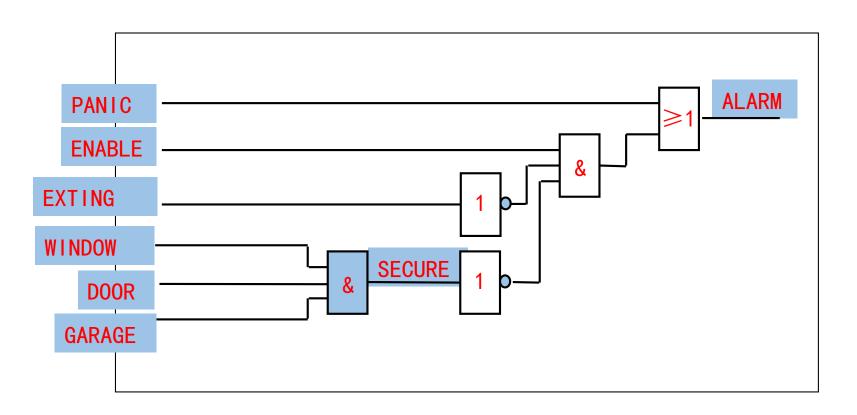

例6: 设计一个房间报警电路。

如果:

①意外事件发生输入PANIC为1;

②使能输入ENABLE为1、出口标志输入EXITING为0、房间没有加密 (SECURE); 则 报警输出ALARM为1。

如果:窗(WINDOW)、门(DOOR)及车库(GARAGE)都是1 则房间加密(SECURE)。

```

ALARM = PANIC + ENABLE • EXITING • SECURE

SECURE = WINDOW • DOOR • GARAGE

ALARM = PANIC + ENABLE • EXITING

• (WINDOW • DOOR • GARAGE)

```

#### 报警电路逻辑图

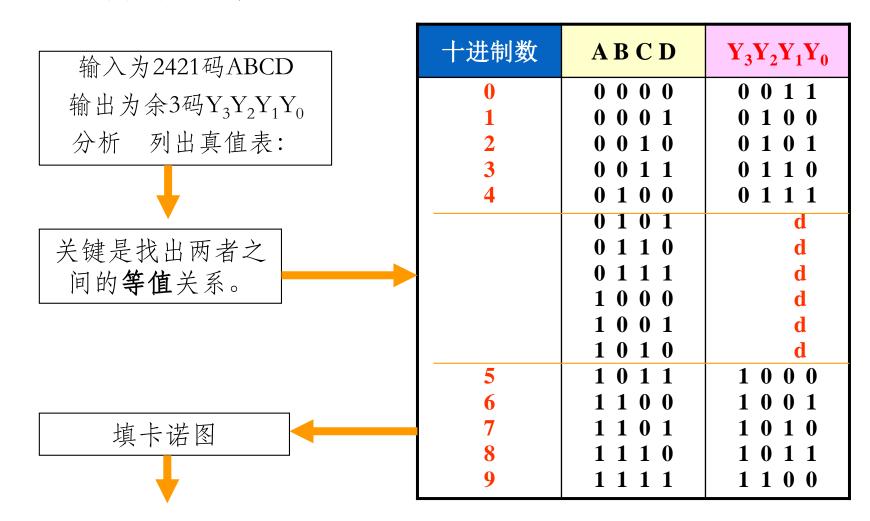

## 例7 码制转换电路

31/44

第一步:填出所有的"d"

| ABCD               | $\mathbf{Y}_3\mathbf{Y}_2\mathbf{Y}_1\mathbf{Y}_0$ |

|--------------------|----------------------------------------------------|

| $0 \ 0 \ 0 \ 0$    | 0 0 1 1                                            |

| 0 0 0 1            | 0 1 0 0                                            |

| 0 0 1 0            | 0 1 0 1                                            |

| 0 0 1 1            | 0 1 1 0                                            |

| _0_1_0_0           | 0 1 1 1                                            |

| $0\ 1\ 0\ 1$       | d                                                  |

| 0 1 1 0            | d                                                  |

| 0 1 1 1            | d                                                  |

| $1 \ 0 \ 0 \ 0$    | d                                                  |

| $1 \ 0 \ 0 \ 1$    | d                                                  |

| <del>1 0 1 0</del> | d                                                  |

| 1 0 1 1            | 1 0 0 0                                            |

| 1 1 0 0            | 1 0 0 1                                            |

| 1 1 0 1            | 1 0 1 0                                            |

| 1 1 1 0            | 1 0 1 1                                            |

| 1 1 1 1            | 1 1 0 0                                            |

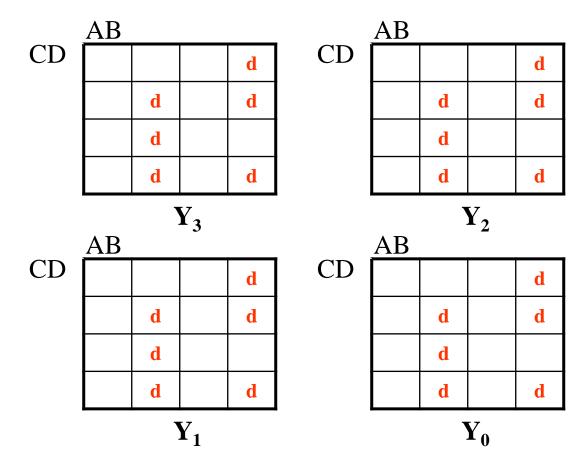

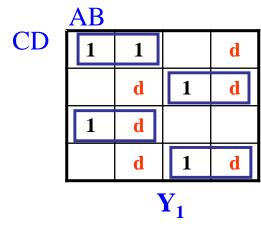

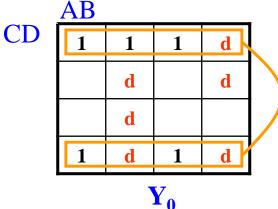

第二步:按Y<sub>3</sub>、Y<sub>2</sub>、Y<sub>1</sub>和Y<sub>0</sub>分别填完卡诺图

$\mathbf{Y}_3$

|    | <u>AB</u>      | _ | _ |   |

|----|----------------|---|---|---|

| CD | 1              | 1 |   | d |

|    |                | d | 1 | d |

|    | 1              | d |   |   |

|    |                | d | 1 | d |

| ·  | $\mathbf{Y_1}$ |   |   |   |

CD

CD

| AB |   |   |   |

|----|---|---|---|

|    | 1 |   | d |

| 1  | d |   | d |

| 1  | d | 1 |   |

| 1  | d |   | d |

$\mathbf{Y_2}$

| AB |   | _ |   |

|----|---|---|---|

| 1  | 1 | 1 | d |

|    | d |   | d |

|    | d |   |   |

| 1  | d | 1 | d |

|    |   |   |   |

$\mathbf{Y_0}$

| ABCD                                               | $\mathbf{Y}_3\mathbf{Y}_2\mathbf{Y}_1\mathbf{Y}_0$ |

|----------------------------------------------------|----------------------------------------------------|

| 0 0 0 0                                            | 0 0 1 1                                            |

| $0\ 0\ 0\ 1$                                       | $0\ 1\ 0\ 0$                                       |

| $0\ 0\ 1\ 0$                                       | 0 1 0 1                                            |

| $0\ 0\ 1\ 1$                                       | 0 1 1 0                                            |

| _0 1 0 0                                           | 0111                                               |

| 0 1 0 1                                            | d                                                  |

| 0 1 1 0                                            | d                                                  |

| 0 1 1 1                                            | d                                                  |

| 1 0 0 0                                            | d                                                  |

| 1 0 0 1                                            | d                                                  |

| <del>1 0 1 0 -                              </del> | d                                                  |

| 1011                                               | $1 \ 0 \ 0 \ 0$                                    |

| $1 \ 1 \ 0 \ 0$                                    | 1 0 0 1                                            |

| 1 1 0 1                                            | 1 0 1 0                                            |

| 1 1 1 0                                            | 1 0 1 1                                            |

| 1111                                               | 1 1 0 0                                            |

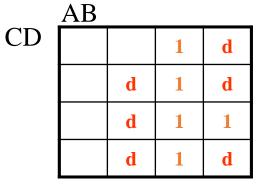

第三步: 找出最小覆盖并写出最简表达式

|    | AB             |   | _ |   |

|----|----------------|---|---|---|

| CD |                | 1 |   | d |

|    | 1              | d |   | d |

|    | 1              | d | 1 |   |

|    | 1              | ф |   | d |

| !  | $\mathbf{Y_2}$ |   |   |   |

$$Y_3 = A$$

$$Y_2 = \overline{AB + AC + AD} + BCD$$

$$Y_1 = \overline{A \oplus C \oplus D}$$

$$Y_0 = \overline{D}$$

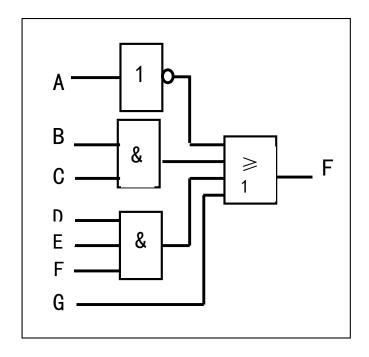

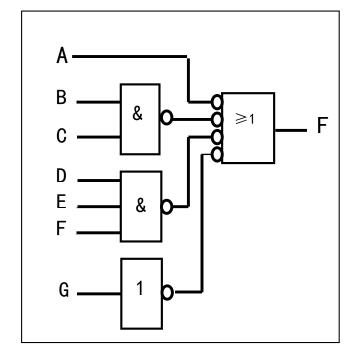

#### 例8 逻辑电路的变换

为了提高电路的速度,提高器件的利用率,从而减少IC的数量、也为了减少外部的连接线和提高电路的可靠性,需要对从逻辑表达式直接画出的逻辑电路图进行变换,尽可能使其用同一类型的输出端带非的门来实现。

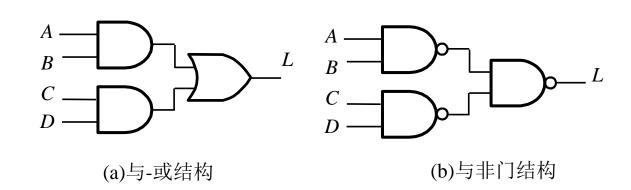

#### (1) "与一或"电路变换为"与非一与非"电路

35/ 44

#### 对应的两个不同的电路如下:

$$F = \overline{A + BC + DEF} + G$$

$$= \overline{A BC DEF G}$$

#### (2)"或一与"电路变换为"或非一或非"电路

例

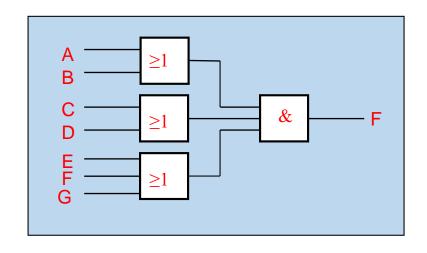

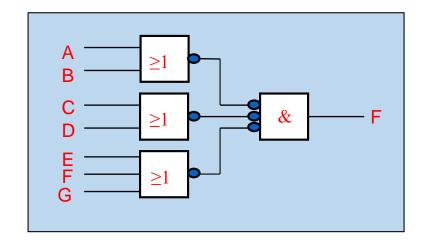

$$F = (A + B)(C + D)(E + F + G)$$

=  $(A + B)(C + D)(E + F + G)$  (原函数二次求反)

=  $(\overline{A + B}) + (\overline{C + D}) + (\overline{E + F + G})$  (运用反演规则)

=  $(\overline{A + B}) \bullet (\overline{C + D}) \bullet (\overline{E + F + G})$  (运用反演规则)

#### (3) "与一或"电路变换为"与或非"电路

例

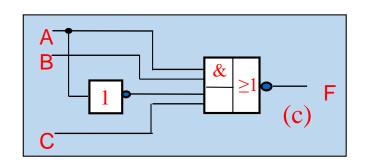

$$F = \overline{AC} + \overline{AB}$$

(a)

$= \overline{\overline{AC} + \overline{AB}}$  (b)

$\overline{F} = \overline{\overline{AC} + \overline{AB}}$  (b)

$= (A + C)(\overline{A} + B)$

$= AB + \overline{AC}$

$F = \overline{AB + \overline{AC}}$  (c)

#### 减少集成块的数量 Reduce the Numbers of IC

目前采用的小规模门电路SSI是把几个相同的门封装在同一个集成块中,在逻辑电路中使用的SSI的数目越少,则电路的印刷电路扳的面积、功耗、总成本越小,而可靠性越高。

所以,减少SSI的数目是化简的最终目标。 在实际应用中,对SSI的计算与分立元件的计算不一样。

#### 组合逻辑电路的优化实现

用指定芯片中特定资源实现逻辑函数,使电路的成本低并且工作速度快。因此需要对逻辑表达式进行变换,以减少芯片资源的数目和连线。

#### (1) 单输出电路

$$L = AB + CD$$

$$= \overline{AB \cdot CD}$$

- 相同输入端的与非门比与门和或门所用晶体管少,速度快。

- 图(b)电路最优

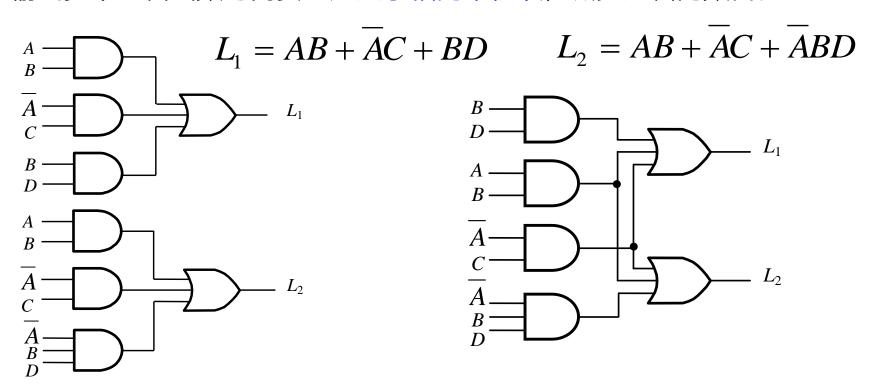

#### (2) 多输出电路

输出多个逻辑函数时需要考虑共享相同乘积项,减少逻辑门数目。

- (a)如果分别实现两个逻辑函数,需要6个与门和两个或门。

- (b)如果考虑相同乘积项,需要4个与门两个或门,如图。

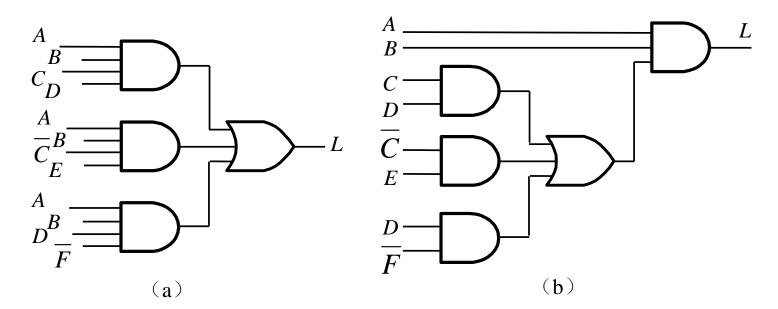

- (3) 多级逻辑电路 当限定逻辑门输入端数目,则需要进行逻辑变换。

- (1) 提取公因子 L = ABCD + ABCE + ABDF

用与门、或门实现时,限定逻辑门的扇入数为3,需要变换成:

$$L = AB(CD + \overline{C}E + D\overline{F})$$

图(a)电路为2级,图(b)为3级,但电路连线减少了。图(a)16根连线,图(b)13根。

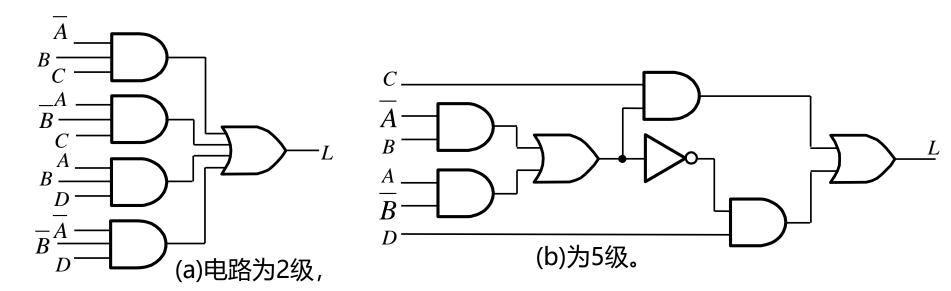

#### (2) 函数分解

$$L = \overline{ABC} + A\overline{BC} + ABD + \overline{ABD}$$

用与门、或门实现时,限定逻辑门的扇入数为3,需要变换成:

$$L = (\overline{A}B + A\overline{B})C + (AB + \overline{AB})D = (\overline{A}B + A\overline{B})C + (\overline{A}B + A\overline{B})D$$

上述变换方法只适合手工化简,当变量数很多时,优化策略写入程序由计算机完成。

# 数字逻辑基础

下一节内容:

# 组合逻辑电路中的竞争与险象