|

序号 |

项目编号 |

项目名称及来源 |

时间 |

角色 |

状态 |

| 21 | 2022YFB4500500 | 超异构软硬件协同计算统一框架(国家重点研发计划项目,重点专项) | 2022.10-2025.09 | 主持 | 在研 |

|

20 |

2022ZDLGY01-08 |

基于异构计算架构的大规模图分析的高性能计算(陕西省重点研发项目) |

2022.01-2024.12 |

主持 |

在研 |

| 19 | CEIEC-2022-ZM02-0245HZ | 2022年人工智能边缘计算芯片项目 | 2022.08-2024.07 | 主持 | 在研 |

|

18 |

J202304020 |

基于RetinaNet的SAR图像的AI加速器设计(北京机电工程研究所) |

2023.01-2023.07 |

主持 |

结题 |

| 17 | 20220540 | 定制化无人机群飞行控制系统开发及调试(光机所) | 2022.03-2022.12 | 主持 | 结题 |

|

16 |

20211284 |

AI智能处理芯片(中电科) |

2021.10-2022.10 |

主持 |

结题 |

| 15 | 20200946 | 无人机群自主协同控制系统开发(光机所) | 2020.01-2020.12 | 主持 | 结题 |

|

14 |

2019B010153003 |

面向自主智能体感知与协作的计算架构和验证研究(广东省重点领域研发计划项目) |

2020.01-2022.12 |

主持 |

结题 |

|

13 |

61773307 |

神经形态计算网络的互连结构和信息组织研究(国家自然科学基金面上项目) |

2018.01-2021.12 |

主持 |

结题 |

|

12 |

2018ZX01028101 |

超算协处理器与强智能终端的智能计算单元(国家核高基重大专项) |

2018.01-2020.12 |

主持 |

结题 |

| 11 | 20170741 | 机动车无人驾驶之深度3D视觉系统 | 2017-2019 | 主持 | 结题 |

|

10 |

2016YFB0200202 |

面向新型众核处理器的应用通信特征分析(国家重点研发计划课题) |

2016-2019 |

主持 |

结题 |

|

09 |

2016M590949 |

面向核自适应滤波算法的计算结构设计与实现(博士后面上基金) |

2016-2019 |

主持 |

结题 |

|

08 |

YESS20150078 |

青年人才托举(中国科协) |

2015-2018 |

主持 |

结题 |

|

07 |

2014AA01A301 |

基于自主处理器的高效能计算机系统研制(863重大项目) |

2015-2016 |

主持 |

结题 |

|

06 |

61303036 |

非均匀众核处理器通讯系统吞吐量优化设计与评估方法研究(国家青年自然科学基金) |

2014-2016 |

主持 |

结题 |

|

05 |

2014A09 |

核自适应滤波器的硬件加速实现与研究(数学工程与先进计算国家重点实验室开放基金) |

2014-2016 |

主持 |

结题 |

|

04 |

/ |

3D显示处理关键技术研究及FPGA实现(陕西省重点实验室青年学术骨干培植项目) |

2014-2014 |

主持 |

结题 |

|

03 |

20130201120024 |

面向高通量非均匀众核处理器的通讯系统设计(教育部博士点基金) |

2013-2014 |

主持 |

结题 |

|

02 |

2013JQ8029 |

新一代众核处理器片上互联网络研究(陕西省自然科学基金) |

2013-2014 |

主持 |

结题 |

|

01 |

2012M521777 |

非均匀众核处理器通讯系统研究(博士后面上基金) |

2012-2014 |

主持 |

结题 |

科研概况 Overview - 任 鹏举

图1:研究方向总览

发展面向人工智能的计算架构和核心芯片具有重要的战略意义,是国家重点支持领域。课题组的科学研究主要围绕先进计算关键软硬件技术、自面向主智能体的智能计算单元、大规模众核处理器通讯系统、神经形态计算/机器学习算法的硬件加速研究与实现、数字多媒体ASIC设计开展,具有多学科交叉以及软、硬件深度协同的特点,与国内外先进科研究机构如:麻省理工MIT、佐治亚理工Gatech、UIUC、波士顿大学BU、英属哥伦比亚大学UBC、弗罗里达大学UF、清华大学、北京大学、浙江大学、中科院等均有很好的项目合作。均有很好的项目合作。本人在人工智能、自动化、计算机、微电子、软件工程等方向招收本科科研实践学生、研究生、博士生及博士后。实验室条件优越、科研经费充足。欢迎有志向、具有自我驱动能力的青年学子咨询报考!

主要研究方向:面向自主智能体的智能计算单元(Intelligent Processing Unit, IPU)是人工智能时代占领战略制高点的核心技术,也是人工智能“硬实力”的体现。课题组主要从事人工智能软/硬件应用系统的研究和开发,主导并完成了8款领域专用芯片的设计和流片(先进制程5nm)。

研究方向一:神经形态计算/机器学习算法的硬件加速研究与实现

- 面向自主智能体的智能计算单元(HiPU系列芯片)

图 2:近5年课题组完成的3款智能芯片的设计

面向自主智能体的神经网络处理器是人工智时代占领战略制高点的核心技术。人机所科研团队顺利完成了包含人工智能算法、高能效计算架构关键技术、系统软件栈、应用支撑框架及典型应用验证等核心技术,实现了计算系统的整体优化。完成了面向开放环境的强智能终端的功能芯片HiPU200的设计和智能驾驶应用验证,该成果于2021年4月成功完成芯片回片验证。基于该架构的FPGA方案已经在我国的多个重点行业得到了推广应用。

图 3:智能计算单元的功能芯片,左图为HiPU200芯片,右图为搭载HiPU200的PCIe板卡

- 28nm HPC+,工作频率1GHz

- 4x4的多核计算架构,采用13个计算核心,整芯片算力13TOPs@INT8

- 两路DDR4 64bits,PCIe3.0x8

- 基于RISC-V自研扩展指令集的DNN加速核心,标量指令多发射乱序执行(SuperScalar OOO)

- 面向AI推理定制向量指令、矩阵指令以及聚合指令,MAC运算效率可达90%以上

- 全局时钟同频不同相(GLAS)、采用自研2D-Mesh片上互连网络(NoC)实现核间数据通讯和核心数目的平滑扩展,NoC采用虫洞路由的4虚拟通道流水线路由器微体系结构设计。

- 支持多核多任务并行、多核单任务并行、以及单核多任务并行等处理方式

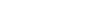

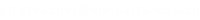

- 基于HiPU200的智能驾驶验证系统

a)障碍物检测识别 b)夜间障碍物识别

c)车道线检测 d)交通灯检测

e)5座电动智能驾驶验证平台 f)7座电动智能驾驶验证平台

图 4:智能驾驶应用验证系统

典型的智能驾驶信息处理任务,将计算密集型及感知层任务划分在强智能终端芯片端,将控制密集型任务划分在CPU端。搭载HiPU200的智能驾驶计算平台在原有的车载计算平台上原位替换英伟达的GPU显卡,运行相同神经网络时,HiPU200的处理速度是RTX2080Ti GPGPU的7.7-35倍(见图3-1、3-2),能效比是其的15-30倍。HiPU200的性能经过第三方权威测试机构(中国电子技术标准化研究院)的评测。

- 神经形态计算算法研究

人脑是迄今为止最有效的信息处理系统,而类脑计算(Brain-inspired computing)则是21世纪科学界的重大挑战之一。以脑认知科学研究成果为基础,借鉴人类感知、认知机理,突破现有计算模式,建立类似人脑的信息组织、存储和处理的计算架构已成为目前计算机科学和人工智能领域备受关注的“大问题”。与多位认知学科教授开展交叉学科研究,以机器视觉信号处理的新型计算架构为切入点,探索构建视觉信息处理开发平台。

图5:从结构连接、功能连接、有效连接的角度分析一种可行的类脑计算架构(From Connection to Cognition)

研究方向二:大规模众核处理器通讯系统研究

当前我们已经进入了多核时代,工业界和学术界都意识到了计算性能的提升依赖于充分的发掘计算的并行性。计算核心越来越多,通过芯片上的互连通信有效地组织和管理这些内核成为目前计算机体系结构的一个关键内容和重要的挑战,我们的研究工作就是围绕这一任务展开。

- 采用可重构技术的众核仿真器(SMART: Simulator for Many-core with Reconfigurable Technique)

半导体制造工艺的进步使得晶体管尺寸进一步缩小,允许设计者在单一芯片上集成几十甚至上千个处理内核。众核处理器的出现将从根本上改变已有的设计和制造方法,丰富的片上计算资源和存储资源都对系统设计带来了前所未有的挑战:如何设计相应的处理单元微体系结构、更好组织管理各处理内核、如何合理的分配计算资源、如何设计层次化的存储结构、如何设计需要满足高带宽、低延时的通讯系统,同时为了满足未来不断发展的计算能力、复杂设计和持续拓展的需求,众核系统还应当具有更好的扩展性和灵活性。该工作重点研究采用可重构技术的众核仿真器相关技术,提供高效、灵活的仿真环境,详尽的量化分析手段指导和帮助研究者更好的学习和研究大规模众核系统。

曾作为联合培养博士生,赴麻省理工学院计算机与人工智能实验室学习交流。其间,与国外学者共同开发了一款开源、并行、可重构众核仿真系统HORNET,该工作先后被MITnews和EETime等国外多家媒体报道,2012年以第一作者将工作发表在IEEE Transaction on CAD。可以在MIT主页下载到源代码:http://csg.csail.mit.edu/hornet/

图6:MITnews和EEtimes新闻报告页面

- 自组织、自适应的高可靠性片上互连网络

围绕面向新型计算架构-千核处理器这一前沿领域,针对异构系统、暗硅以及可靠性问题,在分布式、高通量计算系统开展了较为深入的研究。设计了一种基于通道依赖关系图的容错路由算法,该工作有效地解决了众核芯片容错和负载均衡问题。接着又设计了一种有效避免路由死锁和保证连通性的软硬件解决方案。相关研究成果发表在计算机体系结构顶级期刊,IEEE Transactions on Computers.

图7:片上互连网络研究框架

研究方向三: 数字多媒体ASIC/FPGA芯片以及VR/AR应用:

2005至2017年,课题组完成了多款视频处理ASIC芯片的开发及验证工作,包括:数字视频后处理系列芯片(DTV100,DTV100B/C,DTV110)以及高清立体显示处理芯片HMD100。掌握了多项高清裸眼3D画质处理的核心技术和专利。其中高清立体显示处理芯片HMD100已通过教育部科技成果专家鉴定。

- 视频画质处理芯片:

成功参与完成了6款SoC芯片的设计、流片和验证工作,芯片主要用于多媒体电视信号处理,和头戴式3D显示装置,作为核心成员参与了DTV系列芯片的架构设计、图像增强算法、运动检测算法、DRAM控制器、3D自适应解码器核心IP的设计和开发工作,作为项目总体负责人,指导完成了HMD芯片定义、架构核心算法及开发和设计工作。

图8:6款SoC芯片版图

- 头戴式立体显示芯片:

图9:芯片功能框图和采用自主研发HMD100芯片的头戴式立体显示系统

- 裸眼立体显示关键技术及ASIC实现:

3D显示技术带给人们全新的视觉体验,是今后显示领域势不可挡的主流趋势。3D技术可以使得画面变得立体逼真,使得观看者具有更好的视觉和浸入感体验。人体视觉系统对物体产生立体知觉的成因主要有5种:水晶体的调节、双眼的辐辏角、双眼视差、单眼的运动视差、及聚拢效应。其中,两眼视差所造成的双目立体视觉为主导因素,由于人类的左、右双眼相距6.5公分左右,因此观看物体时的角度略有不同,所接收的影像便会有细微的差异,这个细微的差距,叫做视差(Binocular Parallax)。两个眼睛观察到的两幅具有视差的图像,虽然差距很小,但经视网膜传到大脑里,大脑神经就能利用这微小的差距,产生远近的深度,之后大脑再把双眼接收的影像结合(Convergence),构成具有深度信息的视觉影像。目前立体显示技术大多采用双眼视差的方式。

课题组设计了兼容4/8/9视点可实时合成并输出4K@30Hz立体显示图像的IP核,并采用Xilinx公司型号为XC7K325T的FPGA芯片完成了裸眼立体超高清显示系统的开发和验证工作。已授权美国专利一项、中国发明专利5项,论文发表在IEEE TCASII, ASP-DAC等国际期刊和会议上。

图10:裸眼3D显示处理平台

其它:

- 中铁十八局新建京张铁路四标,实施“东花园隧道段水位控制及远程监控信息自动化解决方案”。该项目是物联网和云计算与传统工业领域应用相结合的典型示范。

- 本科期间,在东力环保设备有限公司(西安研发部)任项目经理,负责DLH-100/200系列垃圾处理设备的智能控制系统电路及程序设计,目前260台设备在青藏线列车上服役。